## Components for Logic

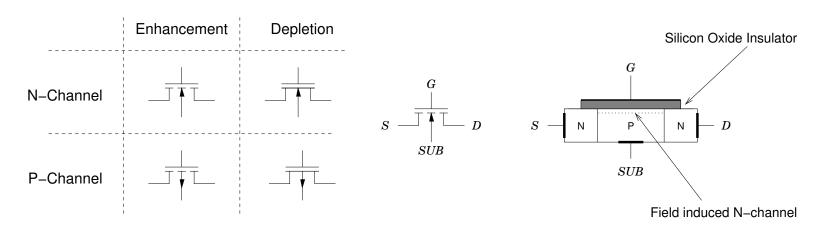

#### **MOS Transistors**

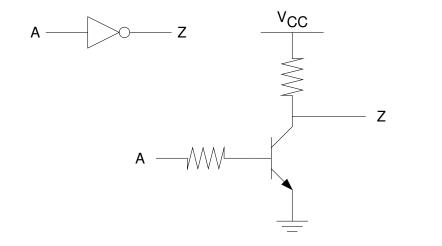

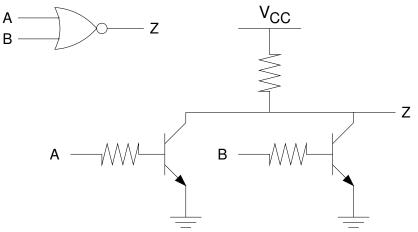

#### RTL Inverter and NOR gate

All functions can be realized with a single NOR base gate.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>NAND gates could be used instead.

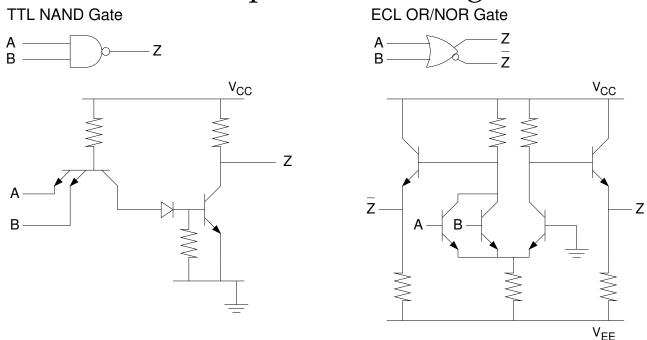

## Other Bipolar Technologies

- TTL gives faster switching than RTL at the expense of greater complexity<sup>2</sup>. The characteristic multi-emitter transistor reduces the overall component count.

- ECL is a very high speed, high power, non-saturating technology.

<sup>&</sup>lt;sup>2</sup>Most TTL families are more complex than the basic version shown here

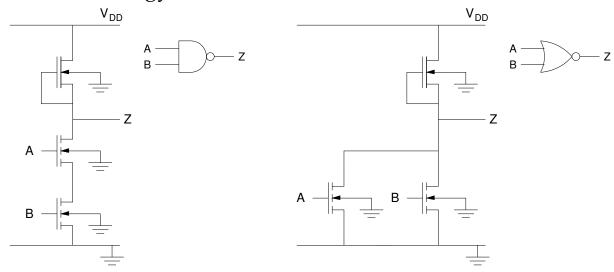

NMOS - a VLSI technology.

- Circuit function determined by series/parallel combination of devices.

- Depletion transistor acts as non-linear load resistor.

Resistance increases as the enhancement device turns on, thus reducing power consumption.

- The low output voltage is determined by the size ratio of the devices.

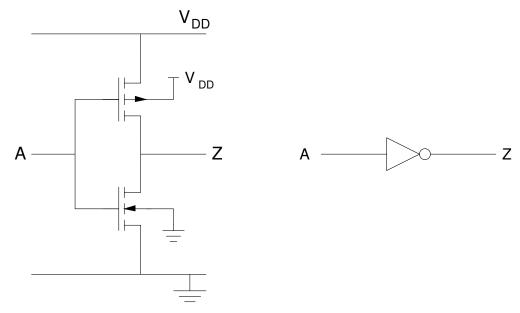

# CMOS logic

CMOS - state of the art VLSI.

- An active PMOS device complements the NMOS device giving:

- rail to rail output swing.

- negligible static power consumption.

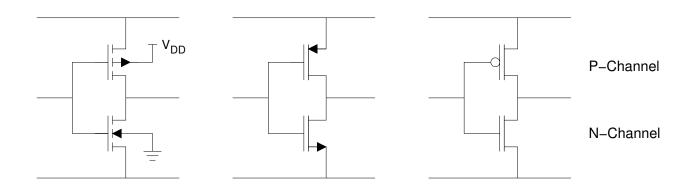

#### Alternative representations for CMOS transistors

Various shorthands are used for simplifying CMOS circuit diagrams.

- In general substrate connections are not drawn where they connect to Vdd (PMOS) and Gnd (NMOS).

- All CMOS devices are enhancement mode.

- Transistors act as simple digitally controlled switches.

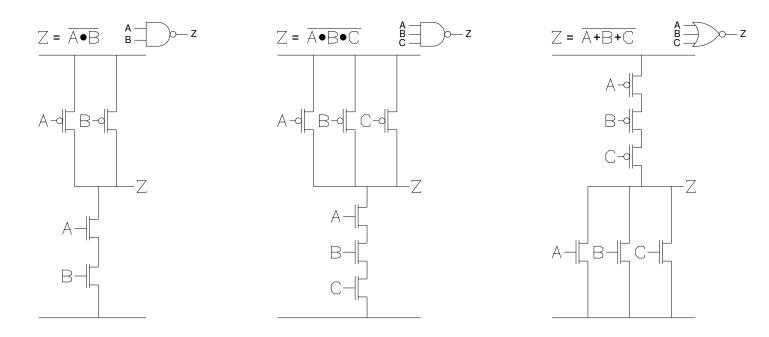

#### Static CMOS complementary gates

• For any set of inputs there will exist either a path to Vdd or a path to Gnd.

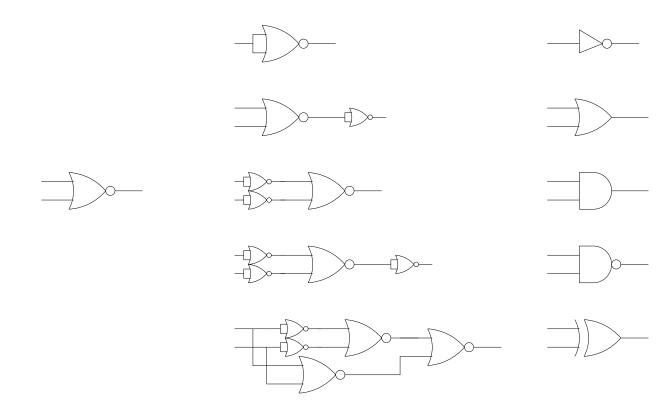

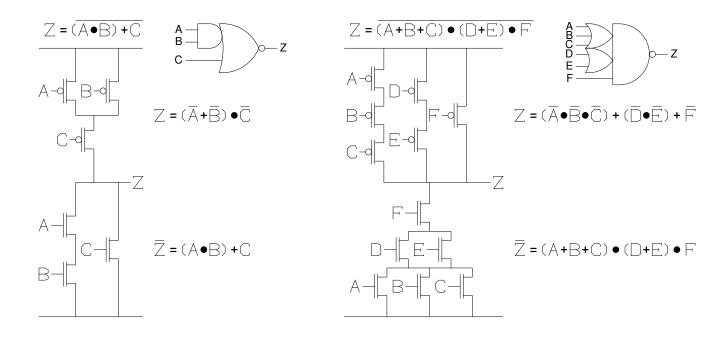

## Compound Gates

- All compound gates are inverting.

- Realisable functions are arbitrary AND/OR expressions with inverted output.

## Compound Gate Example

$\begin{array}{c} \text{Symbol} \\ & \text{A} \longrightarrow \\ & \text{B} \longrightarrow \\ & \text{C} \longrightarrow \\ & \text{D} \longrightarrow \end{array}$

Pull Up Network

$$Z = f(\overline{A}, \overline{B}, \overline{C}, \overline{D})$$

$$Z = \frac{1}{2}$$

$V_{DD}$

\_\_\_\_\_ Z

Pull Down Network

$$\overline{Z} = \int (A,B,C,D)$$

$\overline{Z} = (A \bullet B) + (C \bullet D)$

GND