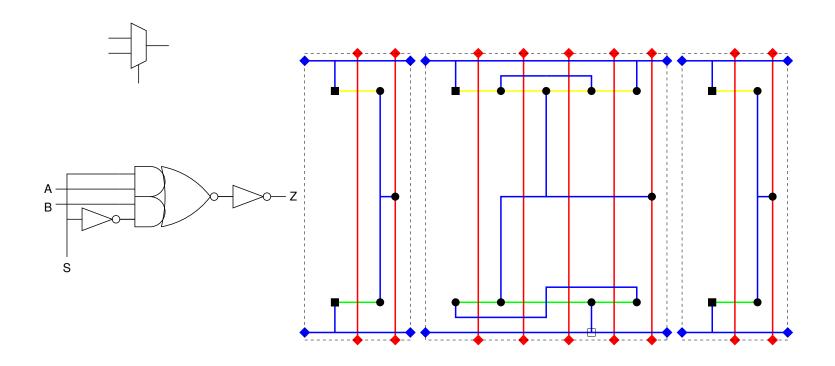

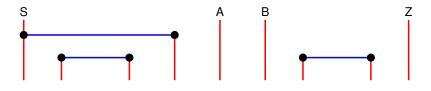

- Gates should all be of same height.

- Power and ground rails will then line up when butted.

- All gate inputs and outputs are available at top and bottom.

- All routing is external to cells.

- Preserves the benefits of hierarchy.

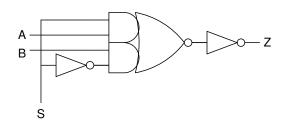

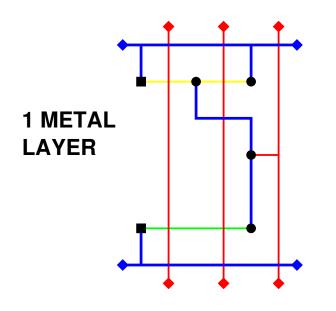

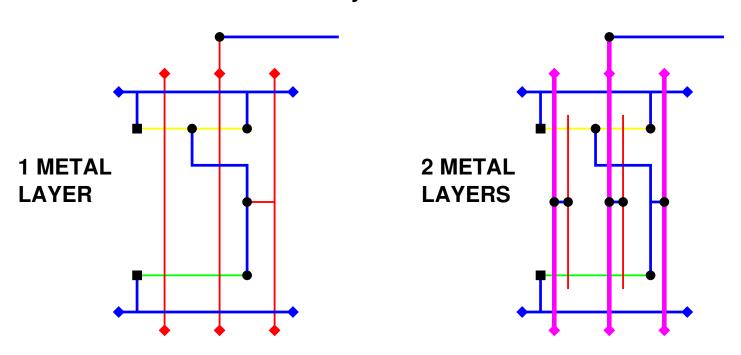

- Interconnect is via two conductor routing.

- In this case Polysilicon vertically and Metal horizontally.

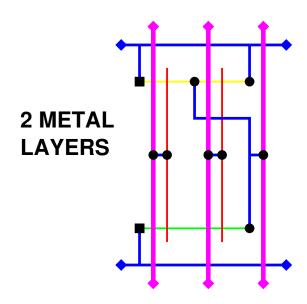

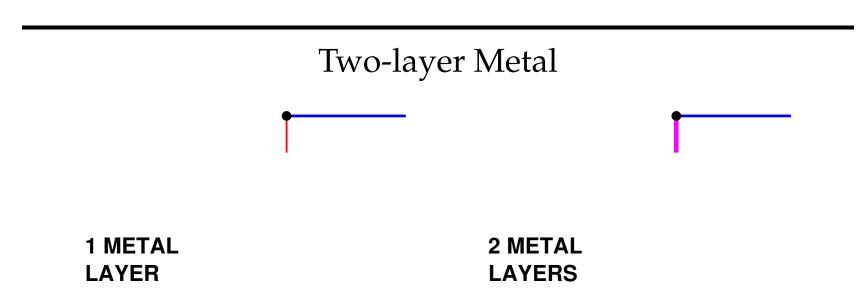

Two-layer Metal

Most modern VLSI processes support two or more metal layers.

The norm is to use only metal for inter-cell routing.

usually Metal1 for horizontal vertical inter-cell routing (and for power rails) (and for cell inputs and outputs).

#### Two-layer Metal

Most modern VLSI processes support two or more metal layers.

The norm is to use only metal for inter-cell routing.

usually Metal1 for horizontal vertical inter-cell routing (and for power rails) (and for cell inputs and outputs).

Most modern VLSI processes support two or more metal layers.

The norm is to use only metal for inter-cell routing.

usually Metal1 for horizontal vertical inter-cell routing (and for power rails) (and for cell inputs and outputs).

Many ICs are designed using the standard cell method.

#### • Cell Library Creation

A cell library, containing commonly used logic gates, is created for a process. This is often carried out by or on behalf of the foundry.

#### • ASIC¹ Design

The ASIC designer must design a circuit using the logic gates available in the library.

The ASIC designer usually has no access to the full layout of the standard cells and doesn't create any new cells for the library.

Layout work performed by the ASIC designer is divided into two stages:

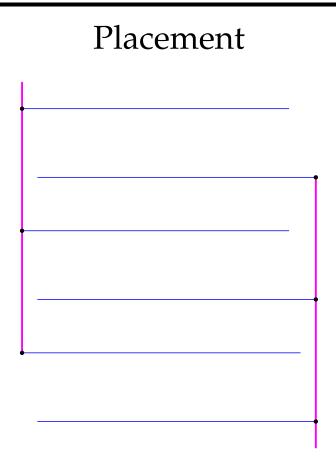

- Placement

- Routing

<sup>&</sup>lt;sup>1</sup>Application Specific Integrated Circuit

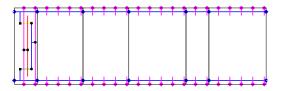

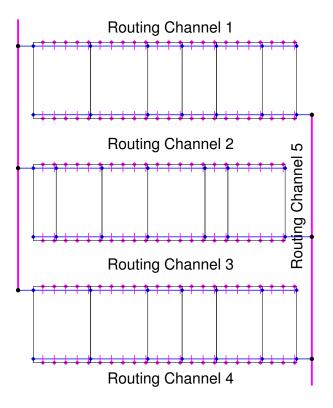

### Placement & Routing

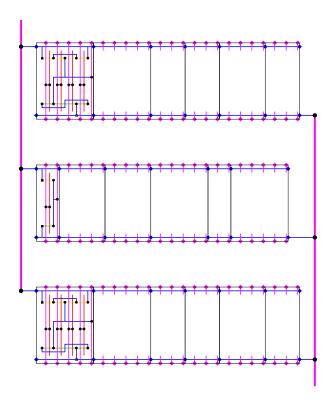

#### Placement

### Placement & Routing

#### Placement

#### Placement

### Placement & Routing

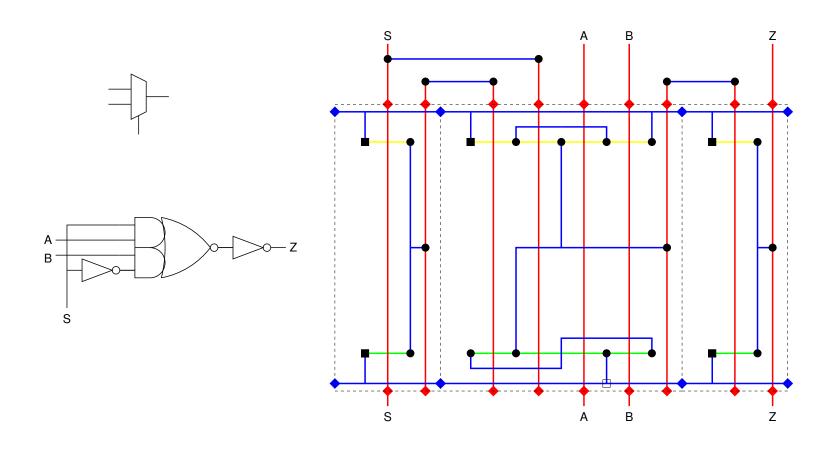

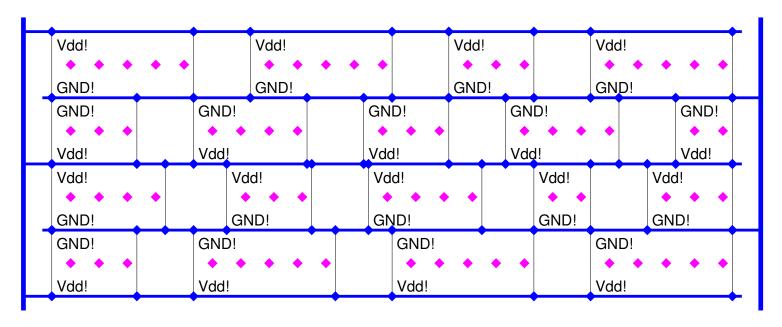

### Inter-Digitated Power and Ground

Inter-digitated power and ground rails can be routed using only one metal layer.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>note – poly may not be used in power routing - see latch-up rules

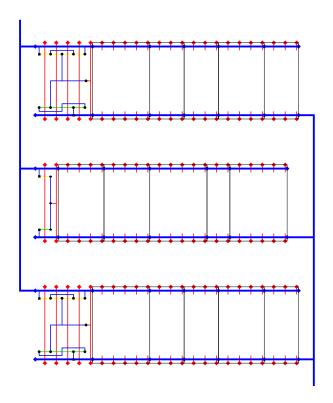

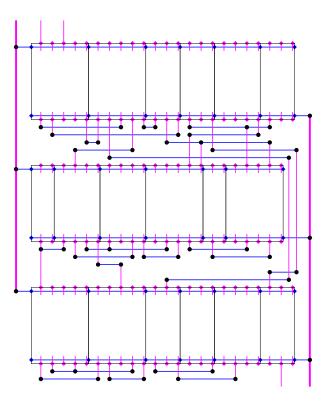

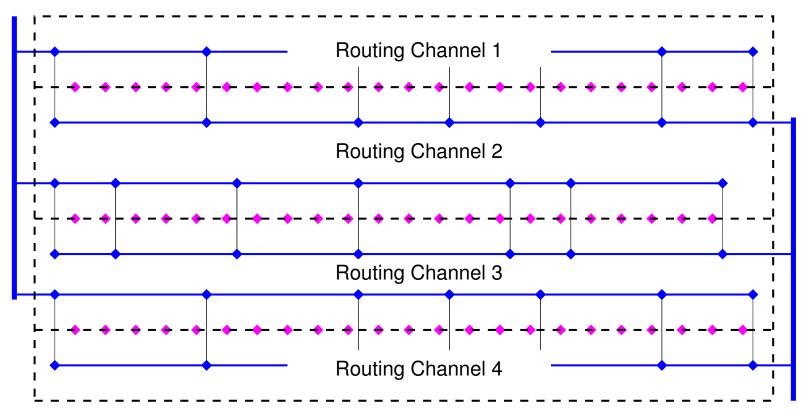

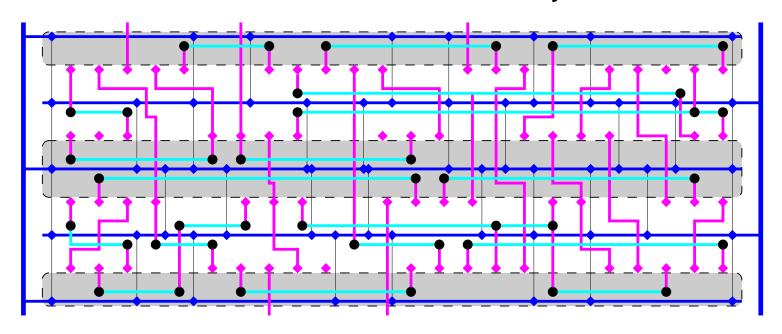

### Routing

#### Placement & Routing

## Routing

### Routing

### Routing

#### Placement & Routing

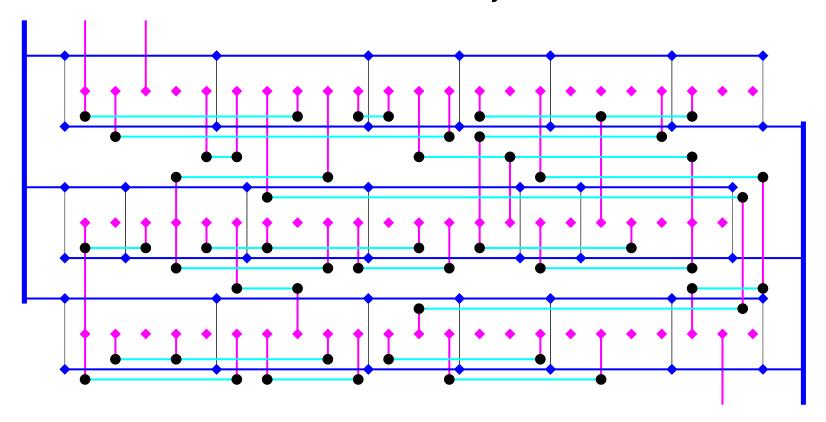

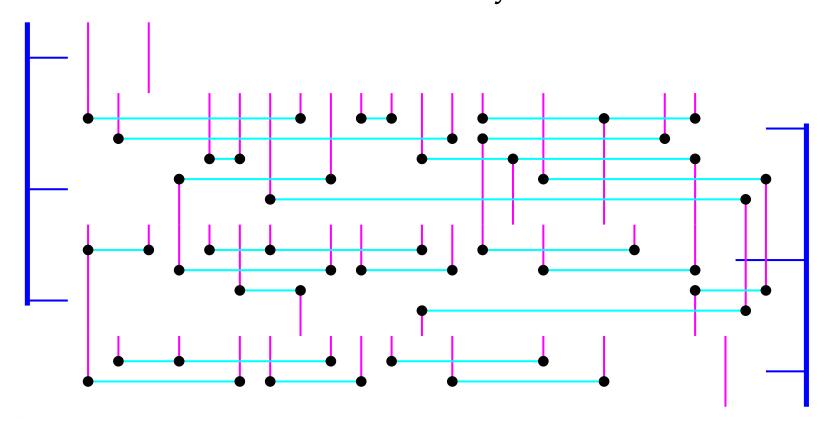

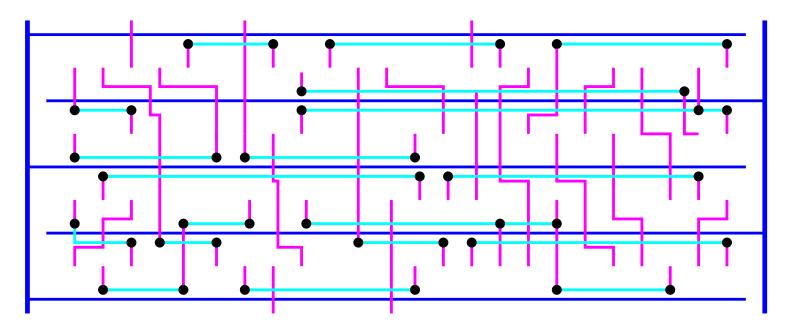

#### Two conductor routing

- Conductor A Conductor B for horizontal vertical inter-cell routing <sup>3</sup>

- This logical approach means that we should never have to worry about signals crossing.

- This makes life considerably easier for a computer (or even a human) to complete the routing.

- We must only ensure that two signals will not meet in the same horizontal or vertical channel.

- Computer algorithms can be used to ensure placement of cells such that wires are short.<sup>4</sup>

- Further computer algorithms can be used to optimize the routing itself.

<sup>&</sup>lt;sup>3</sup>In the two-metal example Conductor A is Metal1 and Conductor B is Metal2

<sup>&</sup>lt;sup>4</sup>In VLSI circuits we often find that inter-cell wiring occupies more area than the cells themselves.

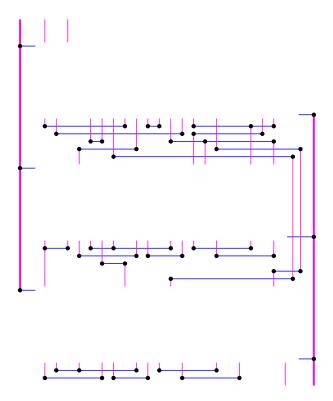

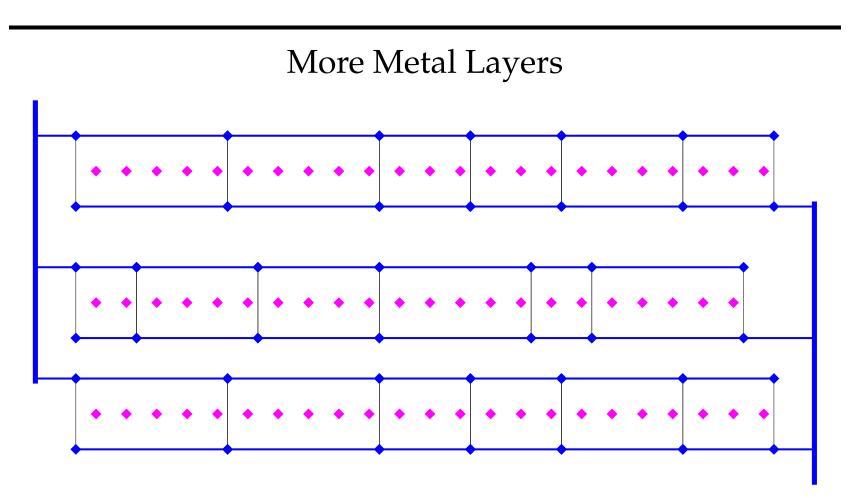

#### More Metal Layers

With three or more metal layers it is possible to take a different approach. The simplest example uses three metal layers.

- Standard Cells

Use only metal1 except for I/O which is in metal2

- Two Conductor Routing Uses metal2 and metal3

#### More Metal Layers

#### More Metal Layers

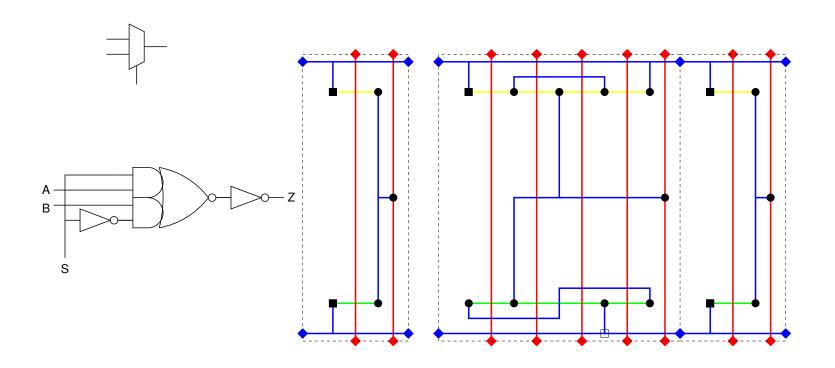

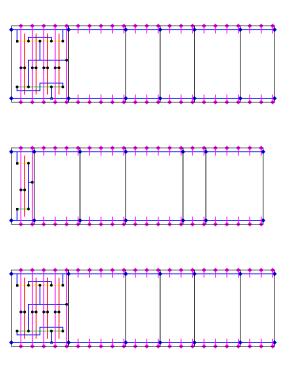

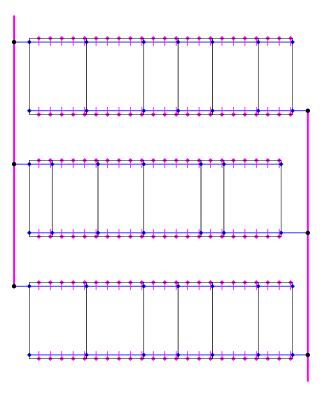

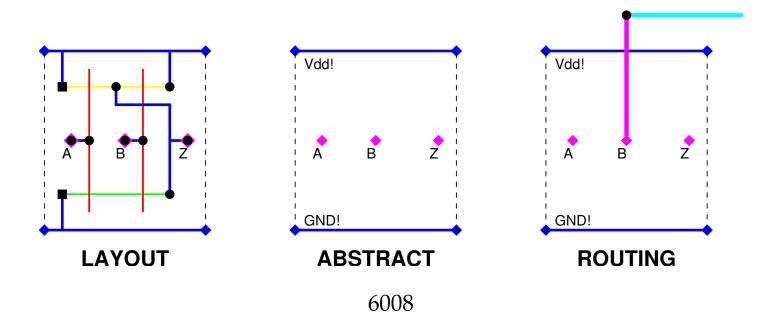

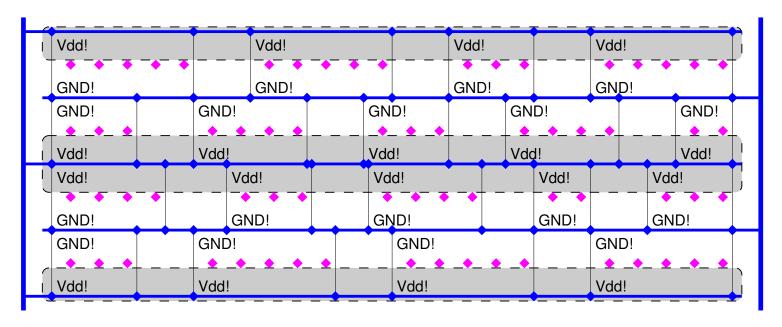

#### Alternative Placement Style

By flipping every second row it may be possible to eliminate gaps between rows. N-wells are merged and power or ground rails are shared.

#### Alternative Placement Style

By flipping every second row it may be possible to eliminate gaps between rows. N-wells are merged and power or ground rails are shared.

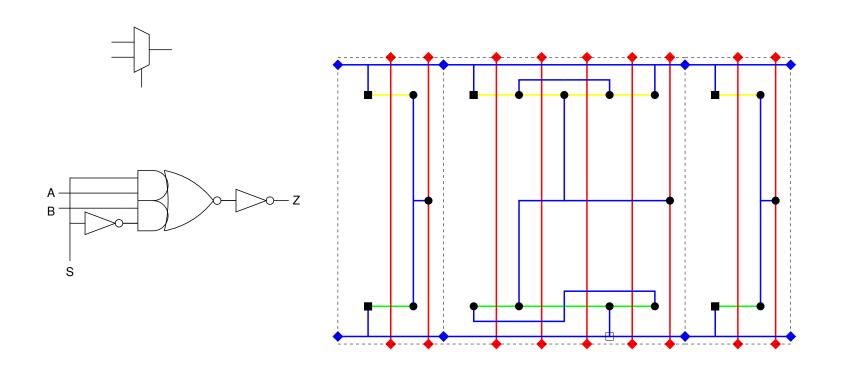

#### Alternative Placement Style

By flipping every second row it may be possible to eliminate gaps between rows. N-wells are merged and power or ground rails are shared.

#### Alternative Placement Style

By flipping every second row it may be possible to eliminate gaps between rows. N-wells are merged and power or ground rails are shared.